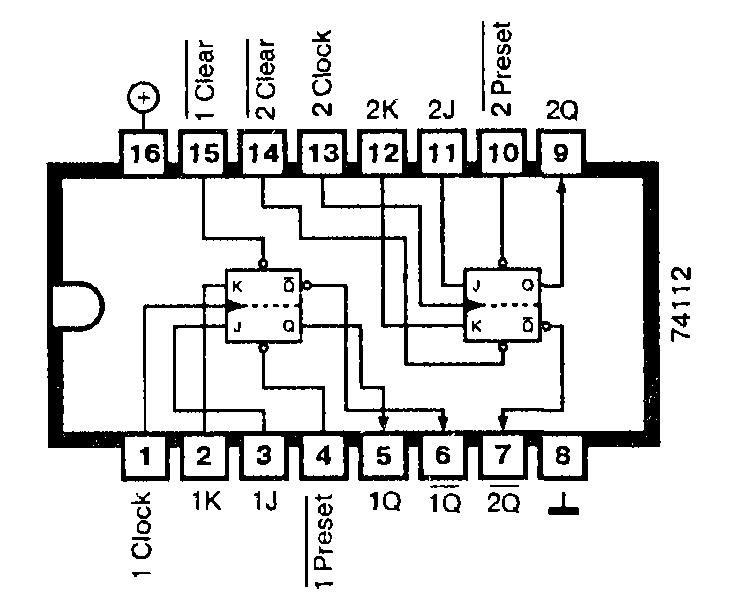

74112 DIP Dual J-K Negative-Edge-Triggered Flip-Flop With Clear AND Preset

25.00 EGP

The 74112 dual JK flip-flop features individual J, K, clock, and asynchronous set and clear inputs for each flip-flop.

Description

- The 74112 is a high speed CMOS DUAL J-K FLIP-FLOP WITH PRESET AND CLEAR fabricated in silicon gate C2MOS technology.

- It has the same high speed performance of LSTTL combined with true CMO Slow power consumption.

- When the clock goes high, the inputs are enabled and data will be accepted.

- The logic level of the J and K inputs may be allowed to change when the clock pulse is high and the bistable will function as shown in the truth table.

- Input data is transferred to the input on the negative going edge of the clock pulse.

- All inputs are equipped with protection circuits against static discharge and transient excess voltage.

Reviews

There are no reviews yet.